COA Tutorial

Basic CO and Design

Computer Instructions

Digital Logic Circuits

Map Simplification

Combinational Circuits

Flip - Flops

Digital Components

Register Transfer

Micro-Operations

Memory Organization

COA_Misc

- Booth's Multiplication Algorithm

- Branch Instruction in Computer Organization

- Data Representation in Computer Organization

- ALU and Data Path in Computer Organization

- External memory in Computer Organization

- Structured Computer Organization

- Types of Register in Computer Organization

- Secondary Storage Devices in Computer Organization

- Types of Operands in Computer Organization

- Serial Communication in Computer organization

- Addressing Sequencing in Computer Organization

- Simplified Instructional Computer (SIC)

- Arithmetic Instructions in AVR microcontroller

- Conventional Computing VS Quantum Computing

- Instruction set used in Simplified Instructional Computer

- Branch Instruction in AVR microcontroller

- Conditional Branch instruction in AVR Microcontroller

- Data transfer instruction in AVR microcontroller

- Difference between Memory-based and Register-based addressing modes

- Difference between 1's complement Representation and 2's complement Representation

- CALL Instructions and Stack in AVR Microcontroller

- Difference between Call and Jump Instructions

- Overflow in Arithmetic Addition in Binary number System

- Horizontal Micro-programmed Vs. Vertical Micro-programmed Control Unit

- Hardwired Vs. Micro-programmed Control Unit

- Non-Restoring Division Algorithm for Unsigned Integer

- Restoring Division Algorithm for Unsigned Integer

- Debugging a Machine-level Program

- Dependencies and Data Hazard in pipeline in Computer Organization

- Execution, Stages and Throughput in Pipeline

- Types of Pipeline Delay and Stalling

- Timing Diagram of MOV Instruction

- Advantages and Disadvantages of Flash Memory

- Importance/Need of negative feedback in amplifiers

- Anti-Aliasing - Computer Graphics

- Bus Arbitration in Computer Organization

- Convert a number from Base 2 (Binary) to Base 6

- Cache Coherence

- EHCI

- Cache Memory and Virtual Memory

- Electrical Potential and Potential Difference

- RAM and Cache

- SIM and RIM instructions in 8085 processor

- Clusters in Computer Organization

- Data Types and Addressing Modes of 80386/80386DX Microprocessor

Multiplexers

A Multiplexer (MUX) can be described as a combinational circuit that receives binary information from one of the 2^n input data lines and directs it to a single output line.

The selection of a particular input data line for the output is decided on the basis of selection lines.

The multiplexer is often called as data selector since it selects only one of many data inputs.

Note: A 2^n-to-1 multiplexer has 2^n input data lines and n input selection lines whose bit combinations determine which input data are selected for the output.

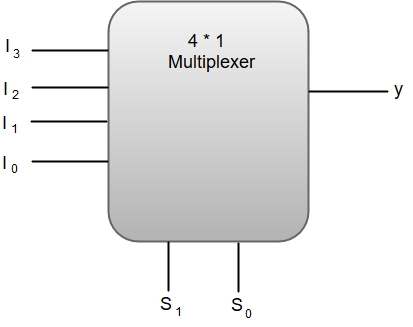

The following image shows the block diagram of a 4 * 1 Multiplexer.

Out of these four input data lines, a particular input data line will be connected to the output based on the combination of inputs present at these two selection lines.

Note: A truth table describing the circuit needs 64 rows since six input variables can have 2^n binary combinations. This will result in an excessively long table. Therefore, a more convenient way to describe the operation of multiplexers is using a function table.

The function table for a 4 * 1 Multiplexer can be represented as:

| S1 | S0 | y |

|---|---|---|

| 0 | 0 | I0 |

| 0 | 1 | I1 |

| 1 | 0 | I2 |

| 1 | 1 | 13 |

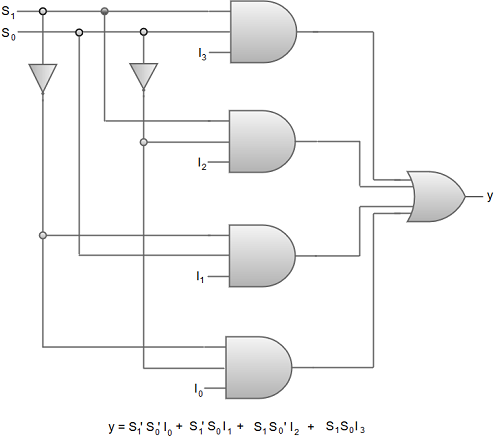

From the function table, we can write the Boolean function for the output (y) as:

y = S1'S0'I0 + S1' S0'I1 + S1S0'I2 + S1S0I3

The above equation for output 'y' can be implemented using inverters, three-input AND gates and an OR gate.

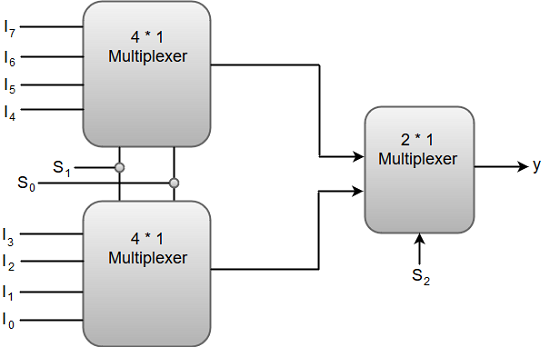

We can also implement higher order multiplexers using lower order multiplexers. For instance, let us implement an 8 *1 multiplexer using two 4*1 multiplexers and a 2*1 multiplexer.

The two 4*1 multiplexers are required in the first stage to get the eight input data lines.

A 2*1 multiplexer is required in the second stage to converge the outputs generated at first stage into a single output.

The following image shows the block diagram of an 8*1 multiplexer designed using two 4*1 multiplexers and a single 2*1 multiplexer.

A set of common selection lines (S1 and S2) are applied to both of the 4*1 multiplexers.

The output generated by both of the 4*1 multiplexers is applied as inputs of the 2*1 multiplexer.

The function table for an 8*1 multiplexer can be represented as:

| S2 | S1 | S0 | y |

|---|---|---|---|

| 0 | 0 | 0 | 10 |

| 0 | 0 | 1 | I1 |

| 0 | 1 | 0 | I2 |

| 0 | 1 | 1 | I3 |

| 1 | 0 | 0 | I4 |

| 1 | 0 | 1 | I5 |

| 1 | 1 | 0 | I6 |

| 1 | 1 | 1 | 17 |