COA Tutorial

Basic CO and Design

Computer Instructions

Digital Logic Circuits

Map Simplification

Combinational Circuits

Flip - Flops

Digital Components

Register Transfer

Micro-Operations

Memory Organization

COA_Misc

- Booth's Multiplication Algorithm

- Branch Instruction in Computer Organization

- Data Representation in Computer Organization

- ALU and Data Path in Computer Organization

- External memory in Computer Organization

- Structured Computer Organization

- Types of Register in Computer Organization

- Secondary Storage Devices in Computer Organization

- Types of Operands in Computer Organization

- Serial Communication in Computer organization

- Addressing Sequencing in Computer Organization

- Simplified Instructional Computer (SIC)

- Arithmetic Instructions in AVR microcontroller

- Conventional Computing VS Quantum Computing

- Instruction set used in Simplified Instructional Computer

- Branch Instruction in AVR microcontroller

- Conditional Branch instruction in AVR Microcontroller

- Data transfer instruction in AVR microcontroller

- Difference between Memory-based and Register-based addressing modes

- Difference between 1's complement Representation and 2's complement Representation

- CALL Instructions and Stack in AVR Microcontroller

- Difference between Call and Jump Instructions

- Overflow in Arithmetic Addition in Binary number System

- Horizontal Micro-programmed Vs. Vertical Micro-programmed Control Unit

- Hardwired Vs. Micro-programmed Control Unit

- Non-Restoring Division Algorithm for Unsigned Integer

- Restoring Division Algorithm for Unsigned Integer

- Debugging a Machine-level Program

- Dependencies and Data Hazard in pipeline in Computer Organization

- Execution, Stages and Throughput in Pipeline

- Types of Pipeline Delay and Stalling

- Timing Diagram of MOV Instruction

- Advantages and Disadvantages of Flash Memory

- Importance/Need of negative feedback in amplifiers

- Anti-Aliasing - Computer Graphics

- Bus Arbitration in Computer Organization

- Convert a number from Base 2 (Binary) to Base 6

- Cache Coherence

- EHCI

- Cache Memory and Virtual Memory

- Electrical Potential and Potential Difference

- RAM and Cache

- SIM and RIM instructions in 8085 processor

- Clusters in Computer Organization

- Data Types and Addressing Modes of 80386/80386DX Microprocessor

De-Multiplexers

A De-multiplexer (De-Mux) can be described as a combinational circuit that performs the reverse operation of a Multiplexer.

A De-multiplexer has a single input, 'n' selection lines and a maximum of 2^n outputs.

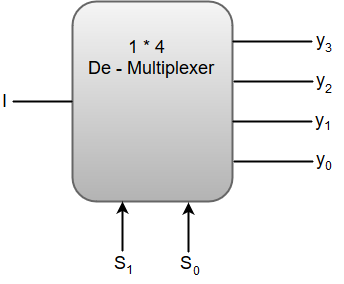

The following image shows the block diagram of a 1 * 4 De-multiplexer.

The function table for a 1 * 4 De - Multiplexer can be represented as:

| S1 | S0 | y3 | y2 | y1 | y0 |

|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | I |

| 0 | 1 | 0 | 0 | I | 0 |

| 1 | 0 | 0 | I | 0 | 0 |

| 1 | 1 | I | 0 | 0 | 0 |

From the above function table, we can write the Boolean function for each output as:

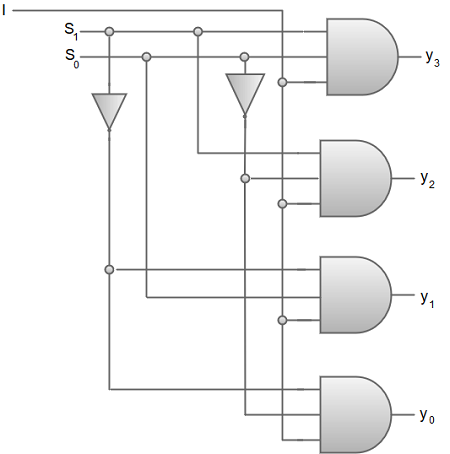

y3 = S1S0 I, y2 = S1S0' I, y1 = S1' S0 I, y0 = S1'S0' I

The above equations can be implemented using inverters and three-input AND gates.

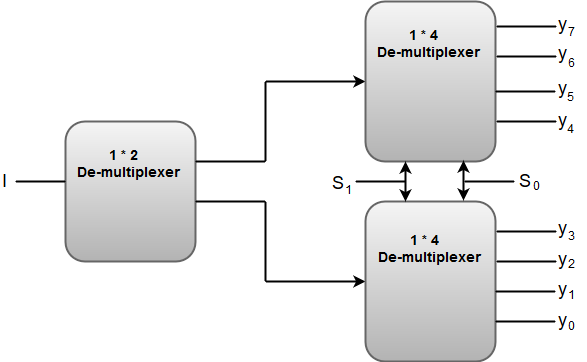

We can also implement higher order De-multiplexers using lower order De-multiplexers. For instance, let us implement a 1 * 8 De-multiplexer using 1 * 2 De-multiplexer in the first stage followed by two 1 * 4 De-multiplexers in the second stage.

The function table for a 1 * 8 De-multiplexer can be represented as:

| S2 | S1 | S0 | y7 | y6 | y5 | y4 | y3 | y2 | y1 | y0 |

|---|---|---|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | I |

| 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | I | 0 |

| 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | I | 0 | 0 |

| 0 | 1 | 1 | 0 | 0 | 0 | 0 | I | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 0 | 0 | I | 0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 | 0 | I | 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 0 | 0 | I | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 1 | I | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

The block diagram for a 1 * 8 De-multiplexer can be represented as:

The Selection lines 'S1' and 'S0' are common for both of the 1 * 4 De-multiplexers.