Computer Components

Computer Memory

Computer Network

Computer Virus

Number Systems

Shortcut Keys

Terms

- What is a Browser

- Google Chrome

- Mozilla Firefox

- Internet Explorer

- Windows

- Computer Ports

- program

- Printers

- Microphone

- Monitor

- Motherboard

- Incognito Mode

- Mouse

- Memory Card

- CD

- ID

- ISO

- character

- server

- Keyboard

- Remote

- webcam

- Data

- URL

- keypad

- hub

- File

- Bytes

- Exabyte

- Gb

- Kilobyte

- Megabyte

- Petabyte

- Terabyte

- What is HDD

- What is SSD

- Memory vs Storage

- Non-volatile memory

- What is M.2 SSD

- How To Reboot A Computer

- Multi-Level Cell

- NAND Flash Memory

- What is the lock screen

- Block Storage

- Universal Serial Bus

- VRAM

- Cloud Hosting

- CompactFlash card

- What is WAP

- Classification of Memory

- Hardware vs Software

- Uses of Computer

- Uses of Internet

- Abacus

- Best Proxy Servers

- SSL VS. TLS

- Web Console

- GPU

- Difference Between LAN and WAN

- SSD and HDD

- Computer

- Data Migration

- JEDEC

- MLC vs. TLC vs. SLC NAND Flash

- VirtualBox Installation

- Num Lock

- PC

- MAC

- Continuous Data Protection

- Persistent Storage

- What is Bit

- Software Definition

- What is a File System

- When was the first computer invented

- How many generations of the computer

- Minicomputer

- Fourth Generation of Computer

- What is a Username

- What is ALU

Questions

Multi-Level Cell

In this topic, we will talk about multi-level cells. The multi-level cell is a type of NAND flash memory that can store more than 1 bit per cell of data. NAND Flash is a form of non-volatile memory that allows data to be stored without power.

Difference between Enterprise Multi-Level Cell and Consumer Multi-Level Cell?

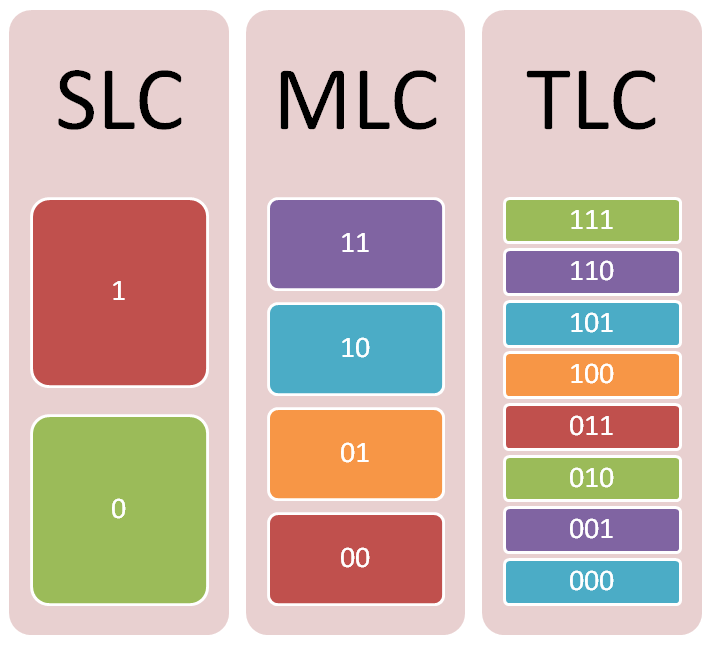

Multi-level cell flash is a center point between single-level cell flash and triple-level cell. NAND flash possesses a finite amount of writing cycles. Since multi-level cell flash is typically less costly than Single-Level Cell flash, it is the preferred solid-state storage memory of consumer-based electronic device makers.

Enterprise multi-level cell drives are designed to handle a greater number of writing cycles with an improved form of multi-level cell flash. Various methods are used to allow the use of eMLC to design inexpensive solid-state drives for enterprises. Algorithms to enhance the unrecoverable bit error rate, flash overprovisioning, wear leveling and amplification of writing are included in these methods.

How multi-level cell flash compares to single-level cell flash?

One disadvantage of multi-level cell flash is its higher bit rate in comparison with NAND flash memory and a single-level cell. The more bits a cell contains, the fewer write cycles it can handle, and the greater the possibility of errors. Single-level cell flash uses NAND memory of best quality, storing 1 bit per cell but always in one of two voltage states programmed, denoted as 0 and 1. Having only two states means that in single-level cell flash allows for fast data analysis and decreases bit error rate. Since SLC flash stores fewer data bits per cell, however, it is typically considered a more expensive form of storage memory than multi-level cell flash.

The ability to multiply multi-level cell flash voltage states decreases manufacturing costs and has increased the use of technology in mobile phones, cameras and USB flash drives. Usually, MLC flash memory cards have a slower transfer speed and use more power. A multi-level cell is divided into four states, defined by the cell's degree of electrical charge. The MLC has two levels, the MLC-3 has eight, and the MLC-4 has 16.

Allowing multiple electrical states can also lead to higher error rates with multi-level flash cells. When a NAND flash cell exceeds its write limit, it will begin to a malfunction that can corrupt data. To make this, vendors tried to solve the issue by developing smarter flash controllers.

Triple-level cell: Successor to consumer flash?

Triple-level flash cells drive NAND flash boundaries. As the title implies, the triple-level NAND cell holds 3 bits of data per flash drive. NAND triple-level cell makes use of developments in geometries of the semiconductor process to give higher densities than planar NAND.

The disadvantage of the triple-level cell flash emerges from the higher error correction required to decode the signal crosstalk resulting from more bits per cell being processed. Triple-level cell SSDs have only made limited appearances as an enterprise flash technology to support high-volume reads.

Flash vendors push boundaries of 3D NAND Technology

Leading flash vendors are breaking the multi-level cell flash limits. The 3D NAND flash memory is a newer flash chip design architecture. Manufacturers stack several layers of memory cells into a vertical structure in 3D NAND. The stacking approach eliminates the electrical interference that occurs while shrinking the cell sizes. Leading 3D NAND flash producers include Intel Corp. Samsung Hynix, SK and Western Multimedia Corp., a companion to Toshiba. The future of the Toshiba-Western Digital relationship is uncertain due to a conflict with Western Digital affiliate SanDisk, which contesting Toshiba's proposed sale to a coalition of Apple Corp., Dell Technologies Resources, Kingston Technology Corp. and Seagate innovations. Based on a 64-layer 3D NAND system architecture, Samsung has disclosed preliminary design for quad-level cell flash.